0%

富果觀點:

- AI 晶片不良成本放大,促使測試前移,篩選良品已成為剛性需求。

- 探針卡往微間距、高針腳數與高頻高速發展,使 MEMS 探針卡需求強勁。

- 產業具備耗材型經常收入與客製化認證門檻,晶片需求強勁下,相關廠商未來持續受益。

引言

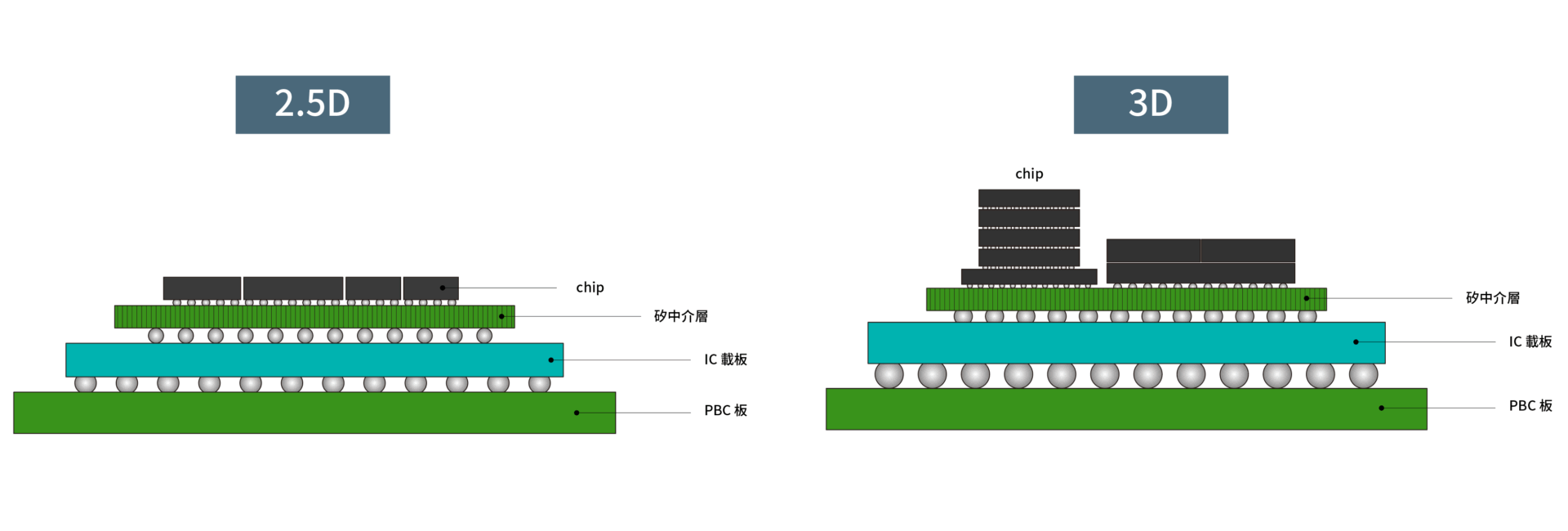

隨著摩爾定律逼近物理極限,半導體製程已難以單靠微縮維持效能躍升,故轉而仰賴 CoWoS 封裝技術,從 2.5D 轉向 3D。然而,當晶片結構從平面走向立體堆疊,雖然突破了原本微縮的極限,卻也讓晶圓測試的複雜度與測試次數大幅提升,主因是隱藏在背後的失誤成本不容小覷,就如同蓋房子蓋到最後才發現一開始的地基或是二樓沒有蓋好,要整棟樓放棄或打掉重蓋的成本都極高。這使得測試的價值與重要性急速上升,相關供應鏈的價值正被重新定位。

2.5D 和 3D 圖示

source : 富果研究部

封裝前先把關,探針卡成為關鍵要角

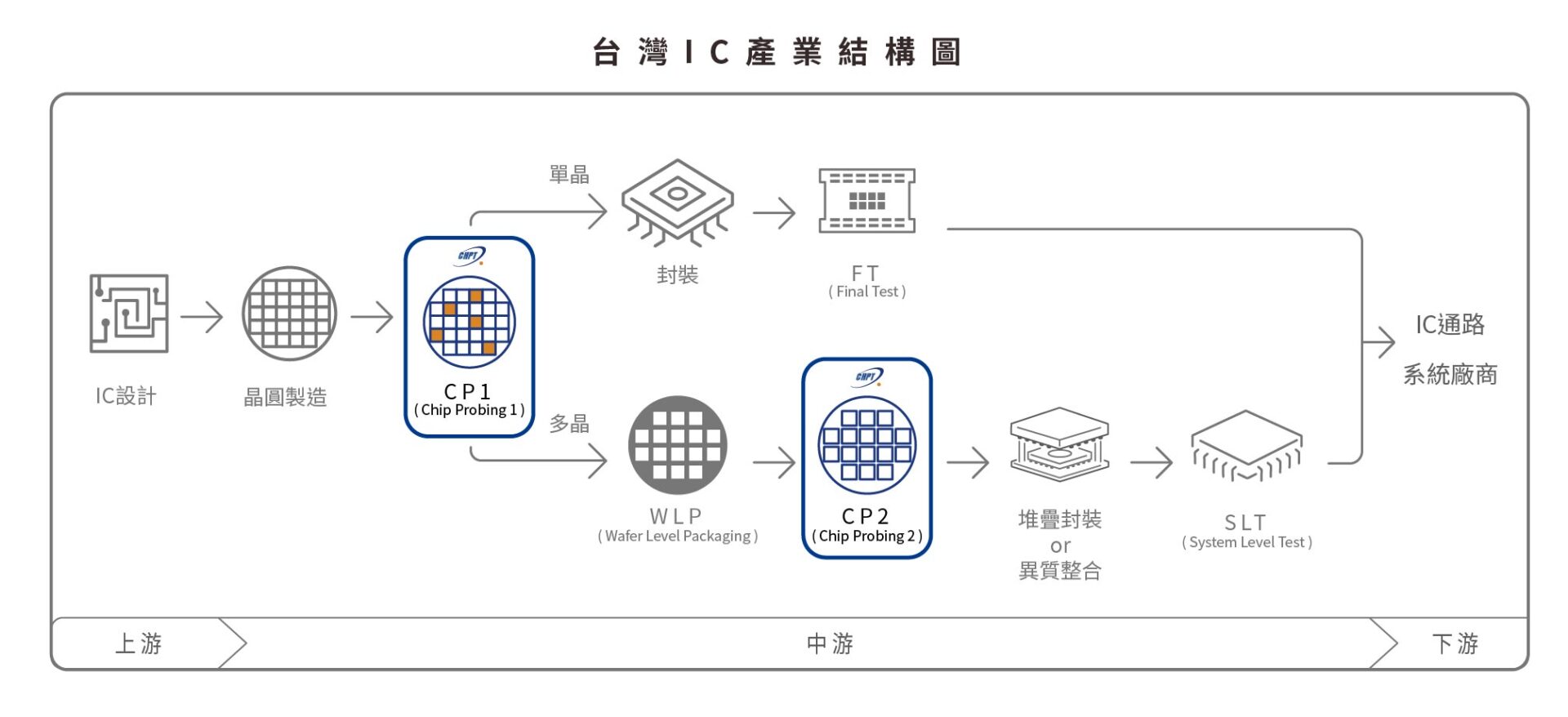

以 NVIDIA、AMD 等高階 AI 晶片為例,在先進封裝與 Chiplet 架構下,一個封裝內往往整合多顆小晶片,在堆疊完後都必須檢測。為了避免最後封裝才發現有損壞,在晶圓封裝前的階段就得開始測試,因為只要其中一顆 Die 存在缺陷,就可能導致整顆昂貴晶片報廢。

晶圓檢測流程

source : 精測

AI 晶片

因此,KGD(Known Good Die,已知良品)篩選成為剛性需求,而扮演關鍵角色的正是探針卡(Probe Card)。 探針卡主要用於晶圓測試階段的關鍵介面工具,透過高針腳