0%

從台積電技術藍圖看出未來先進封裝的三條主要發展路徑

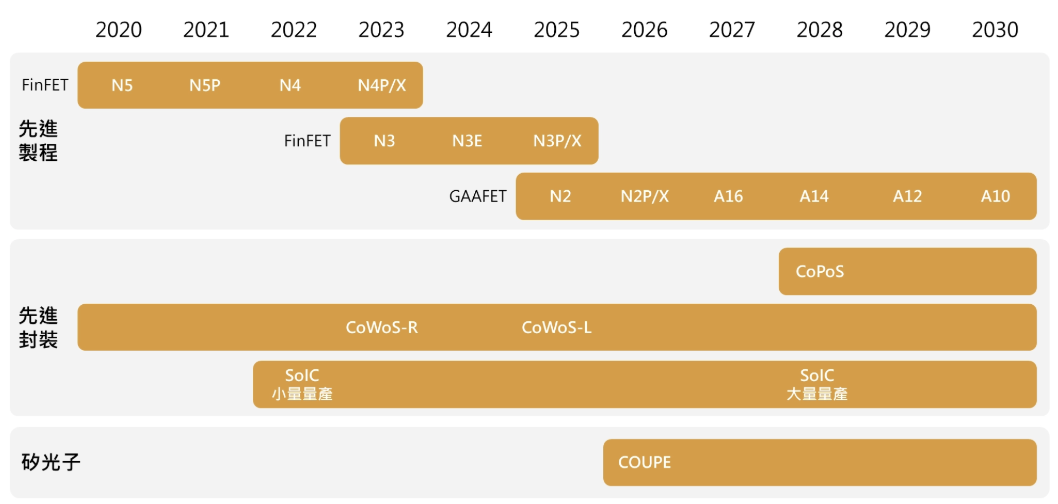

台積電在 2025 年技術論壇上表示,將透過先進製程微縮、先進封裝技術升級、矽光子導入等三大方面演進,以提升晶片效能:

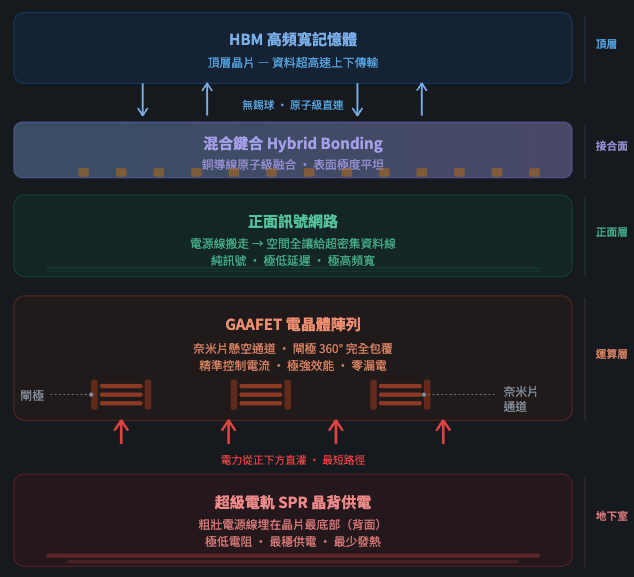

1. 先進製程微縮:在 2 奈米如期於 2025 年量產後,A16 製程預計於 2027 年推出,並同時導入超級電軌(SPR, Super Power Rail)的晶背供電技術,透過晶背供電的方式減少電阻、提升晶片正面線路密度。相關細節可參考富果文章:晶背供電(BSPDN)解析:提升晶片效能的關鍵技術,A14 製程預計於 2028 年推出,並導入混合鍵合(Hybrid Bonding)技術。

資料來源:富果整理

2. 先進封裝技術升級:持續升級 CoWoS 技術,並推動 CoPoS(以玻璃基板取代矽中介層)、SoIC(晶片垂直堆疊)等新封裝技術,以降低封裝成本、提升晶片效能。

3. 矽光子(Silicon Photonics)導入:藉由台積電 COUPE 技術(緊湊型通用光子引擎,Compact Universal Photonic Engine),透過 SoIC-X 封裝將光引擎(PIC, Photonic Integrated Circuit)與電子晶片(EIC, Electrical Integrated Circuit)垂直堆疊、整合,以解決傳統銅線傳輸的電力損耗。

台積電技術預估量產時程

資料來源:台積電、富果

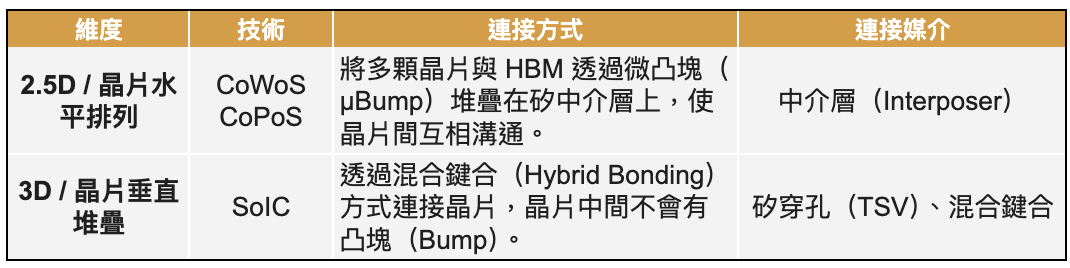

本篇為系列文章的第二篇,第一篇可參考:2026 年先進封裝產業深度報告:台積電 CoWoS-L 迎來爆發,AI 算力重塑臺灣設備供應鏈成長趨勢,說明台積電以 3DFabric 平台整合自行研發的 2.5D 封裝的 CoWoS 技術,以及3D 封裝的 SoIC 技術,確立了未來先進封裝的兩大發展主軸,本篇將先聚焦 2.5D 封裝的關鍵升級——以玻璃基板取代矽中介層的 CoPoS 技術,深入拆解其技術原理、製造挑戰與供應鏈機會;下一篇再進入 3D 堆疊的 SoIC 技術與矽光子整合。

資料來源:富果整理

兩種封裝方式差異為何?如下圖所示,簡單來說,2.5D 封裝為「晶片水平排列」,晶片間溝通透過下方的「中介層」(Interposer)做為溝通