0%

觀點:

1. CoWoS 製程為目前全球 AI 晶片最主流的標準封裝技術:為因應 AI 晶片面積急遽擴張與高功耗需求,台積電的先進封裝重心正全面從傳統的 CoWoS-S(全矽中介層)轉向 CoWoS-L(局部矽互連)製程。

2. 先進封裝技術持續演進,將帶動設備供應鏈產品升級循環。

3. 台積電 2026Q1 法說會表示,未來 3 年資本支出將持續提升,並首次給出跨年度的指引,加速封裝廠產能建置,在台積電供應鏈在地化政策下,臺灣先進封裝供應鏈未來受惠程度、訂單能見度皆提高。

AI 運算架構的物理極限與 CoWoS 封裝的技術演進說明

近年 AI 模型的參數規模已從千億級別躍上升至數兆級別 ,算力的瓶頸早已不再僅限於邏輯晶片(Logic Die)內部電晶體密度的微縮(製程微縮),而是轉移到了「資料傳輸頻寬」與「記憶體容量」的限制。而台積電所研發的 CoWoS 技術,將高頻寬記憶體(HBM)與圖形處理器(GPU)或客製化運算晶片(ASIC)以極短的物理距離整合在同一封裝內,成為業界突破物理極限的重要解方 。

要快速了解 CoWoS 封裝是什麼,在先前的文章有提到先進封裝興起原因、CoWoS 製程等,可參考:【產業報告】台積電獨大的 CoWoS 先進封裝是什麼?為何是 AI 運算發展關鍵?的內容。

CoWoS 全名為「Chip-on-Wafer-on-Substrate」,為台積電研發的封裝技術,將晶片(Chip)先橫向堆疊在中介層(Interposer)後,再堆疊在基板(Substrate)上。對比在 CoWoS 技術誕生前,晶片間的溝通需要透過 PCB 連結,而 CoWoS 技術可以讓晶片間傳輸距離縮短,達到更快速度、更大頻寬、更高容量的需求,使得 CoWoS 符合 AI 時代晶片的高效運算與傳輸的技術需求。

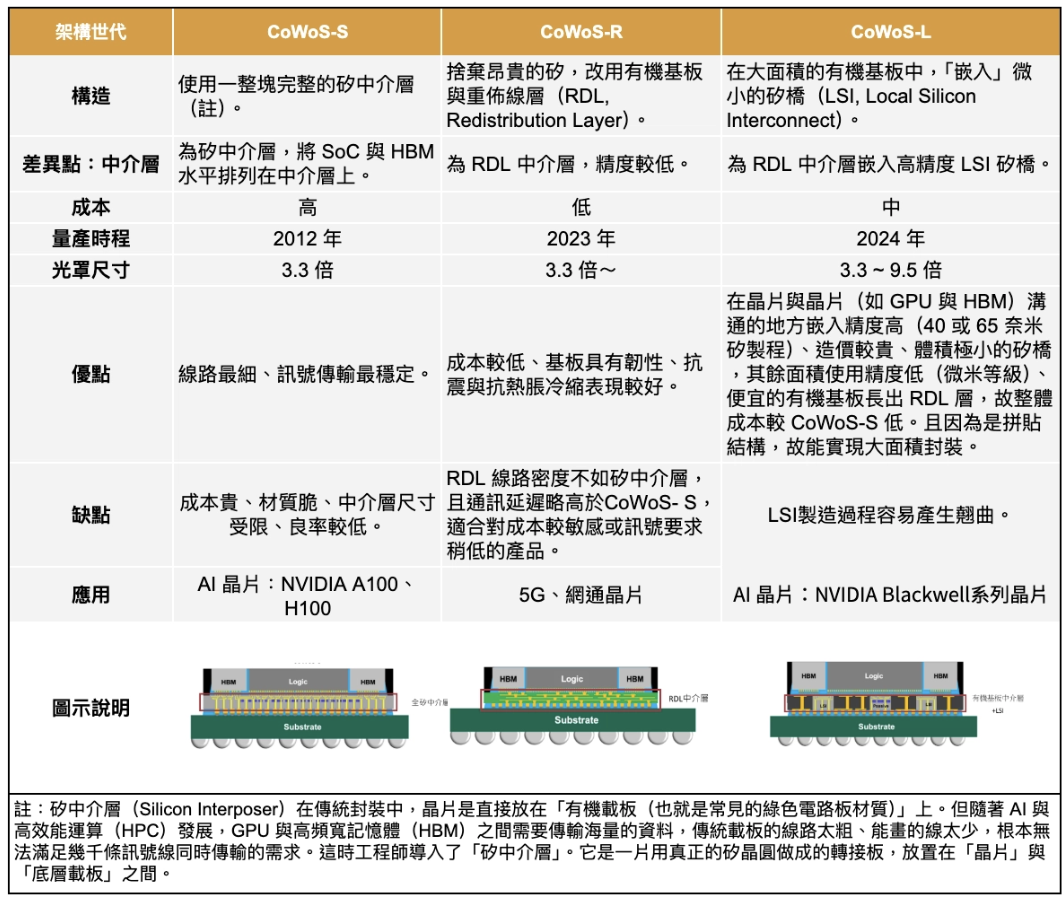

台積電根據「中介層」材質與結構的不同,演進出三種技術,可想像成在不同的地基上蓋房子,不同地基的成本、效率皆不同。

資料來源:富果整理

過去 3 年封裝技術由 CoWoS-S 轉向 CoWoS-L

起初台積電封裝 AI 晶片所使用的技術為 CoWoS-S,近期逐步轉向 CoWoS-L,為了解這項轉變的原因,首先,讓我們需先理解一下 CoWoS-S 在技術發展上遇到的瓶頸:

1. 早期 AI 晶片使用 CoWoS-S 製程,「S」代表矽中介層(Silicon Interposer),中介層整片皆採用矽材料,材質較易脆裂、製造成本高昂,且當晶片數量