0%

近期的 AI 風潮帶動了 Nvidia H100 GPU 的需求大增。而其中,H100 即採用台積電的 2.5D CoWoS 封裝技術。本篇報告將分析先進封裝產業及潛在受惠廠商。

富果觀點

- 摩爾定律趨緩下,先進封裝為下個半導體發展關鍵,預計未來 6 年 CAGR+22.9%

- 先進封裝需求在 AI 帶動下快速成長,主要技術掌握在先進製程晶圓廠

- 台積電、Intel 兩大廠技術最為領先,高資本支出建構高產業進入門檻

- 台積電先進製程+封裝一條龍整合,目前獲大多 IC 設計廠採用。其中 CoWoS 已成 AI 晶片標配

- CoWoS 未來幾年將大幅擴產,相關設備商可直接受惠,然近期股價大多已超前反應

摩爾定律趨緩下,先進封裝為下個半導體發展關鍵,預計未來 6 年 CAGR+22.9%

一般來說,在相同面積下的 IC 晶片要增加效能有兩種方式:

- IC 設計改良。

- 半導體製程微縮,在相同面積的晶片下塞入更多電晶體。

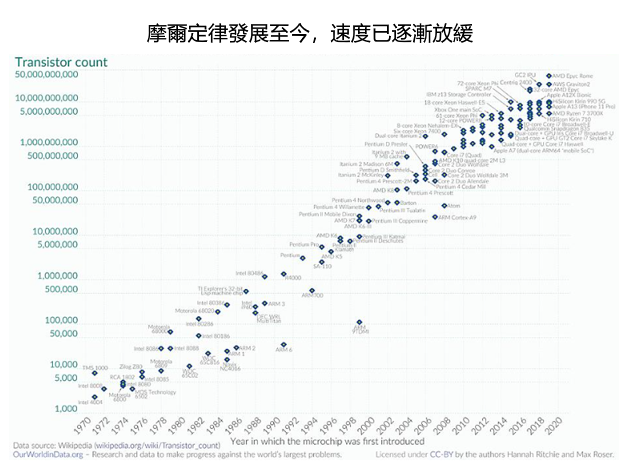

然而,摩爾定律走至今日已漸趨極限,由下圖可看出,雖然摩爾定律仍持續,但製程演進的速度明顯趨緩。以台積電來說,從 7nm 到 5nm 花了 2 年,但從 5nm 走到 3nm 共花了 3~4 年。

Source:維基百科

Source:維基百科

因此,可異質整合的先進封裝(Advanced Package)就成為下個半導體的發展重點。透過 Chiplet(小晶片)模式,以及晶片間的立體堆疊,增加晶片的效能。根據 Yole 研調,先進封裝市場將於未來幾年快速成長,至 2028 年市場規模達 245 億美元,6 年 CAGR+22.9%。並逐漸取代傳統封裝市場。

先進封裝需求在 AI 帶動下快速成長,主要技術掌握在先進製程晶圓廠

先進封裝亦即將處理器、記憶體等多個晶片用堆疊的方式封在一起,增加處理器與記憶體間讀寫效能表現,對如 5G、AI 等要求低延遲、高傳輸速度的應用甚為關鍵。

有別於傳統封裝是先將晶圓切割為一片片的晶片後才封