0%

台積電 (2330)做為全球最大的晶圓代工廠,市佔率高達 50% 以上,舉凡 Apple、高通、華為、AMD、博通、NVIDIA 等世界級公司都是他的客戶,不但如此,它掌握著將近 500 間公司的訂單,因此對整個半導體業可以說是牽一髮動全身。同時 台積電 也佔了 台股 加權指數近 24% 權重,甚至在 ETF 0050 當中,台積電更是佔了約 40% 的權重,所以有興趣投資 0050 的各位更應該要瞭解。

今天我們藉由分析台積電就可以了解 2020 年整體半導體產業的展望及加權指數、0050 的走勢。在這個系列我們將會分兩篇文章來深入分析台積電,上篇會聚焦於半導體產業的分析,下篇則藉由廠房、客戶及財務面來分析它的營運展望。

在開始前,你可能會想先看過「用白話文看懂 IC 產業!加碼5G時代的潛力IC封測名單」。

接著看完本篇文章你將會了解:

- 台積電 的股權結構和經營團隊分析

- IC 製程中的微影製程(photolithography)是什麼?

淺談 EUV 在 5 奈米時代後的重要性- 如何分析 台積電 的競爭優勢

- 台積電未來繼續稱霸市場的可能性

台積電(TSMC)由張忠謀先生於 1987 年成立,其總部位於台灣新竹科學園區。主要從事晶圓代工及先進封裝業務,也是目前全球唯一將進入 5nm 量產的廠商。2019 年所代工的產品應用佔比約為 Smart Phone 45%、 HPC 32%、IoT 8%、車用 5%。客戶遍佈北美洲(60%)、中國(20%)及歐亞(20%)等全球各地。

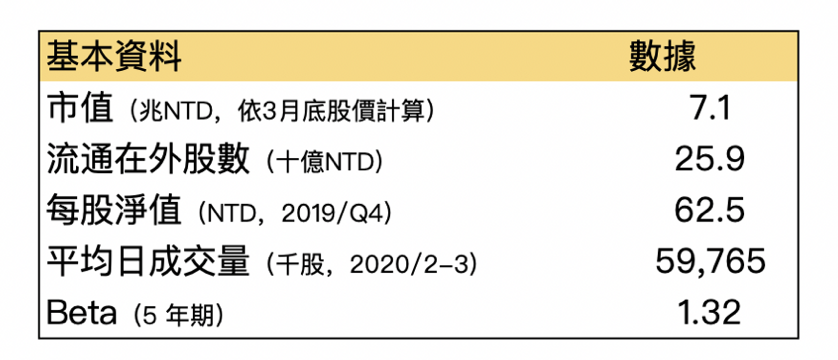

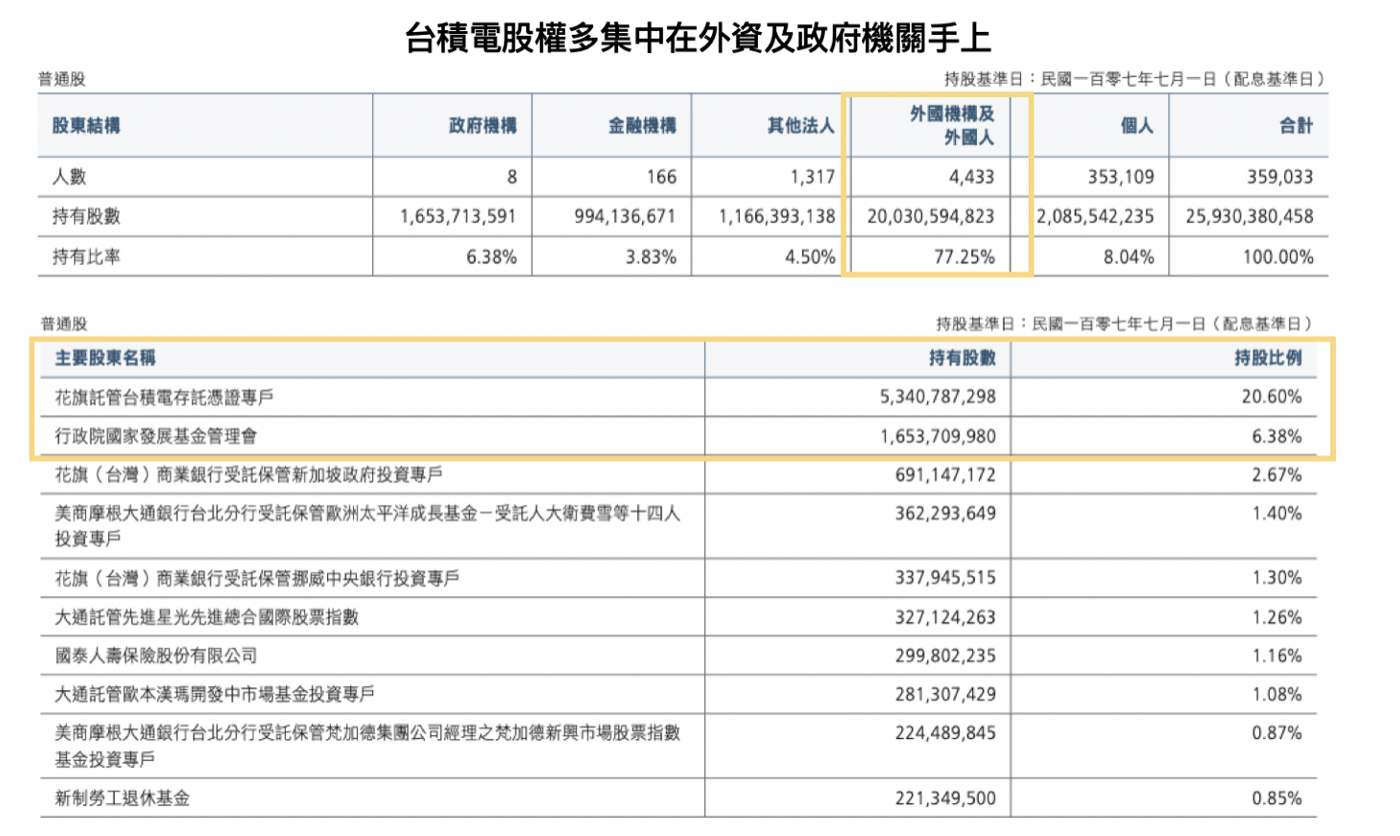

台積電股本大,但股權結構穩定

2019 年底台積電總股本約為 2,590 億元新台幣,股權結構方面,約有 77% 股份集中在外資手上,第一大股東為花旗託管台積電存託憑證專戶(ADR,美國存託憑證,亦即在美國發行的台積電股票,投資人多半為外資)持股 20%,第二大股東為行政院國發基金,持有約 6.4% 股份。另外以持股多寡來看,有 90% 以上的股份都集中在千張以上大戶的手中,由以上資訊可知台積電股權的幾個特色:

- 外資的動向將主導著台積電股價走勢,因此參考外資券商報告的產業觀點相對重要

- 可以用前一日 ADR 的股價漲跌作為預測台積電股價走勢的參考

- 台積電背後有國發、勞退等國家基金在撐腰

- 股權集中,籌碼穩定,持有 400 張以上大戶持股比超過 92%,且個人持有之比例僅佔 8%。

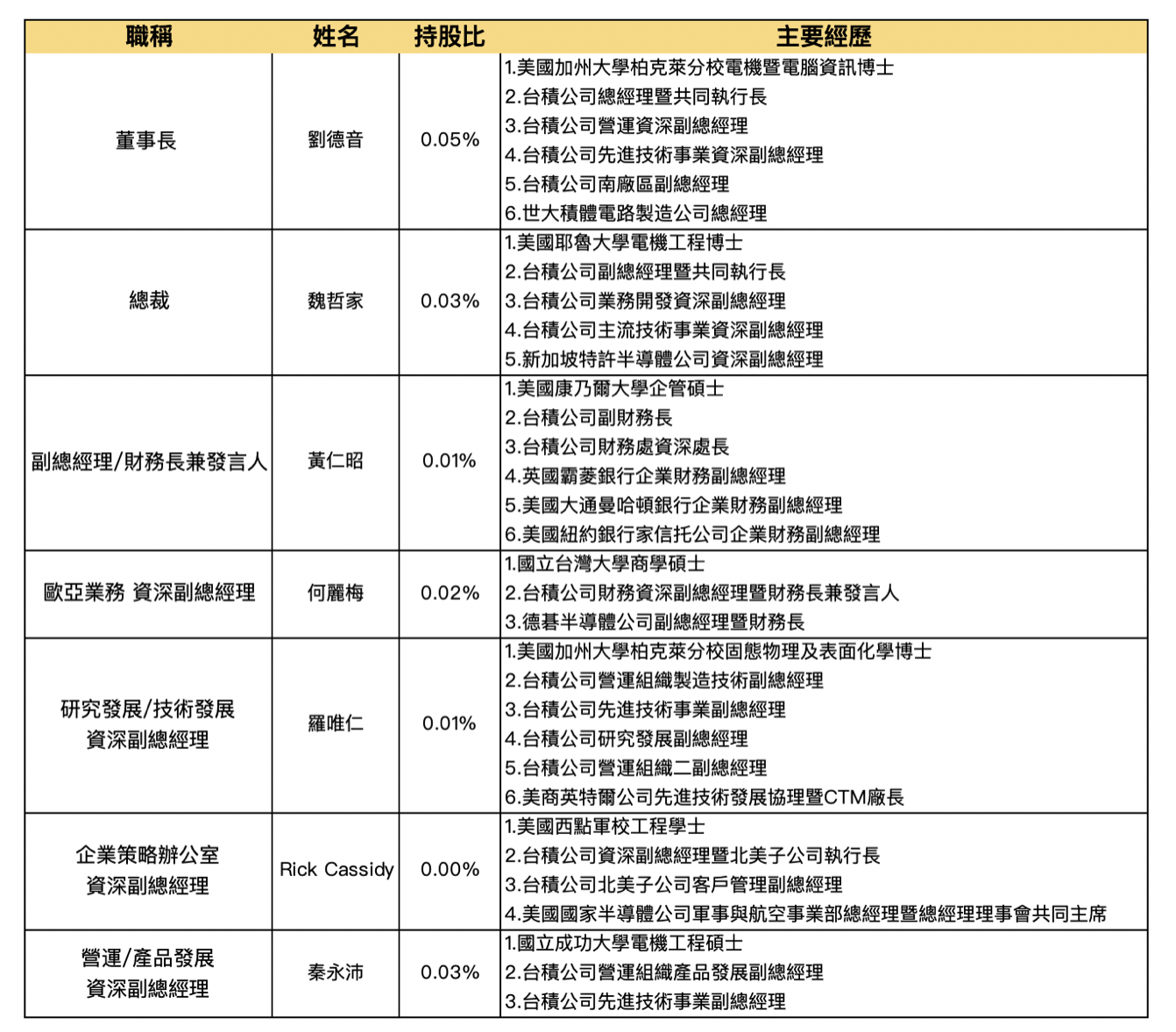

經營團隊資歷完整

台積電的經營團隊大多都擁有多年的半導體產業相關經驗,多數班底為張忠謀時代即培養多年之老將,董監及經營團隊合計持股比約為 0.4%(已扣除國發基金)。

製程微縮至 10nm 以下技術

立即註冊會員閱讀全文10 秒註冊解鎖完整報告

10 秒註冊解鎖完整報告

每週更新,精準掌握投資決策

成為會員繼續閱讀全文,再享每週更新獨家研究報告與多項富果投資研究工具!

- 精選研究報告完整時事短評、法說會備忘錄

- 技術圖表多種投資分析工具與指標

- 筆記功能速記投資心得與重要筆記

- 自訂版面客製喜歡的看盤版面