晶背供電產業前景

摩爾定律一直是推動半導體產業發展的重要參考,它揭示了隨著時間的推移,在積體電路(IC)上所容納的電晶體(Transistor)數量就要翻倍,因此,為達到這個目標,目前最為主流的兩個發展路徑就是:

(1)製程持續微縮:從先進製程最早的 7nm,一路下降至 5nm、3nm、2nm,甚至到以埃米(angstrom,Å,0.1 nm)為單位的 A16 製程。透過不斷縮小閘極尺寸,力求將更多的電晶體塞到 IC 裡面,以得到更強大的晶片。

(2)發展先進封裝:除了把電晶體縮小外,透過將晶片水平或是垂直的堆疉,以取得在相同面積下更多的電晶體數目,這是在後摩爾時代(製程微縮已漸漸接近物理極限)下,最重要的解法之一。

而台積電就是透過掌握上述兩種重要的製程解方,成為世界最大且最強的半導體製造公司。

這篇文章,主要是從製程微縮的角度,來探討並預測下一代製程節點的特色與發展方向,同時判斷在新的 below 2nm 製程發展過程中,為什麼晶背供電值得注意,以及當中有什麼投資機會。

FinFET(鰭式場效電晶體)已在 3nm 走入終局,2nm 開始後,是 GAA FET(gate-all-around)的天下

從台積電跨入先進製程以來(below 10nm),FinFET 一直是先進製程的主要技術方向,而台積電透過持續發揮學習曲線的精神,一路在先進製程的良率上持續領先對手,不論是 7nm、5nm 或 3nm,都在市場上獲得極大的成功。

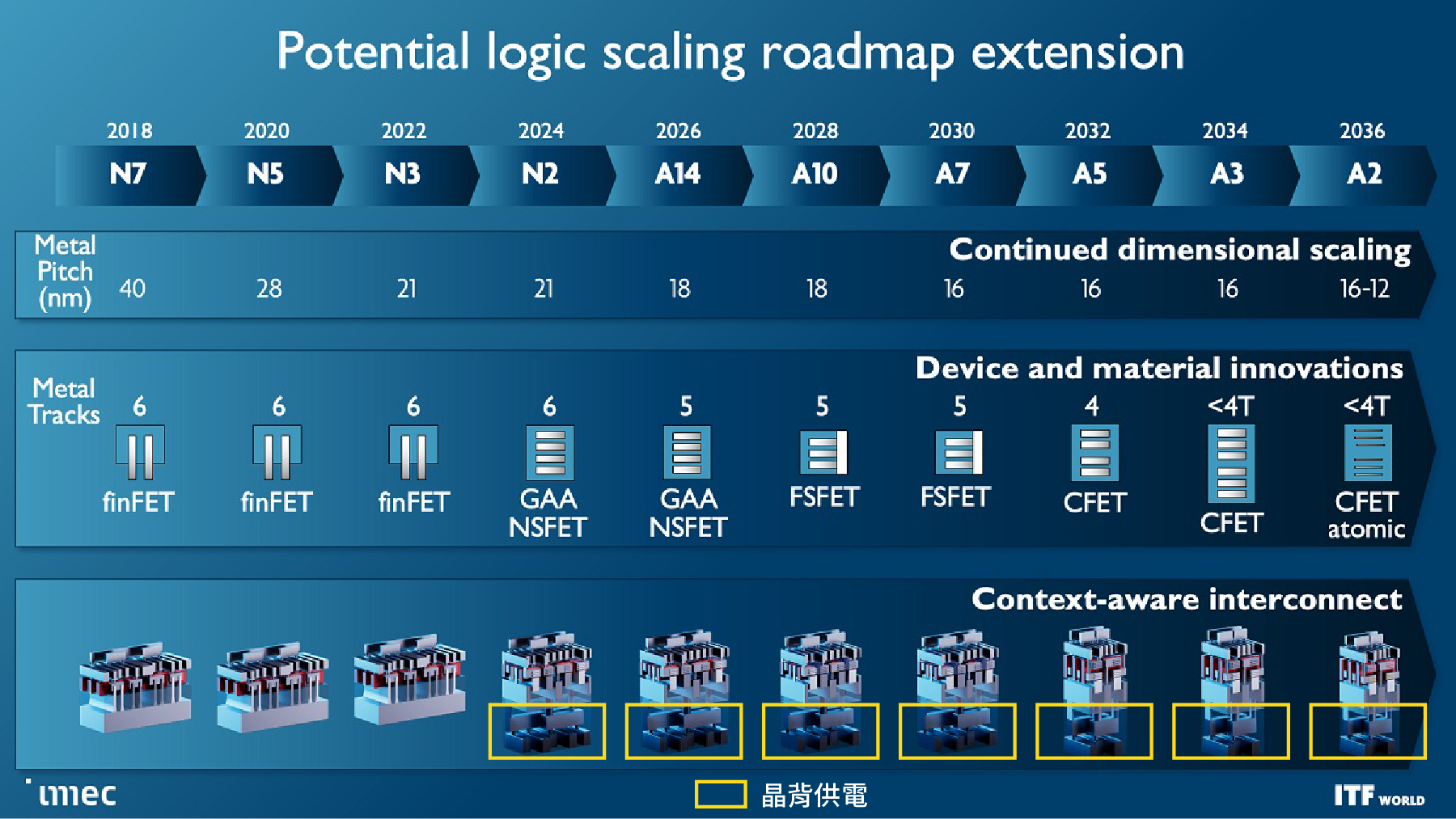

然當走入 2nm 以下時,FinFET 就不敷使用了,必須要進化成所謂的 GAA FET(業界主流的 GAA FET是採 Nanosheet 結構,三星最早是在 3nm 製程上使用;Intel 稱其為 RIBBONFET),判斷未來接下來至少 5 個世代的製程,都同樣會以 GAA FET 為基礎向下發展。下圖展示了未來 10 年的技術發展路徑,即使到了 CFET (complementary FET)時代,仍然是以 GAA 的結構進行製程上的堆疉。

資料來源:imec

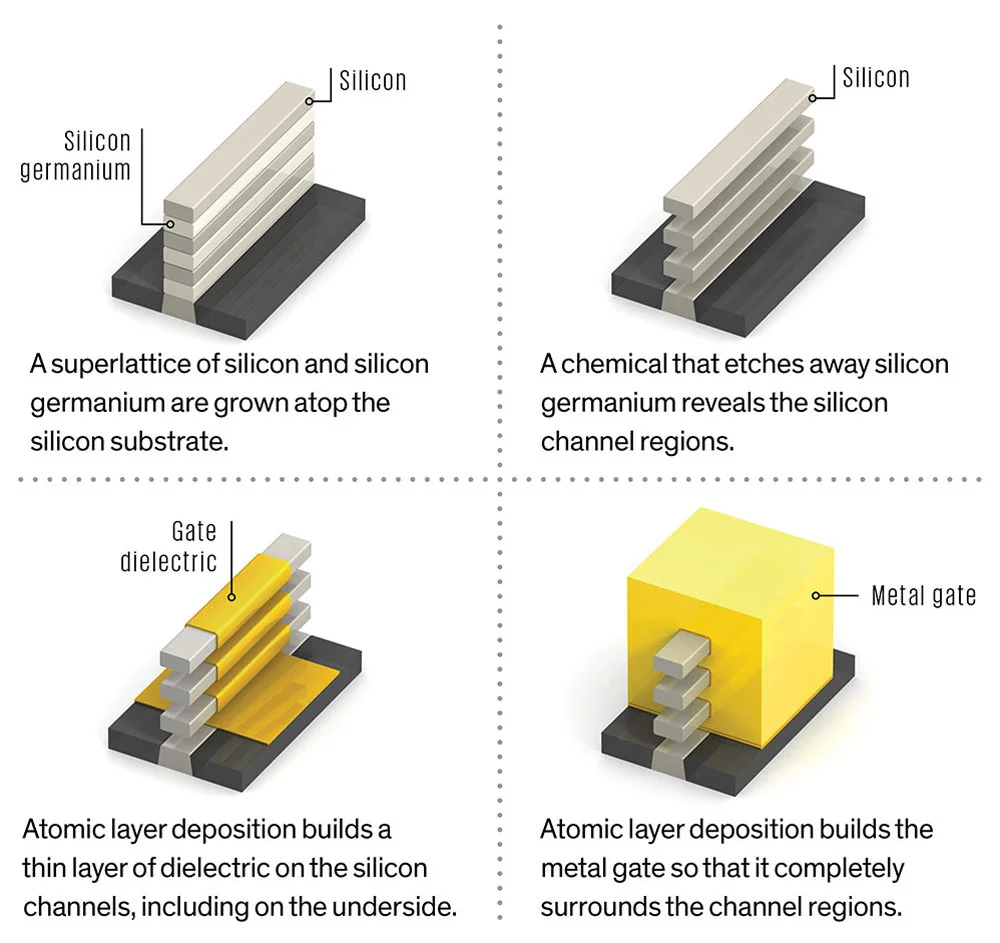

透過觀察,GAA 結構在製程上最大的特色在於將一片片的 Nanosheet(si),包在一層 high-k 的介電材料(dielectric)中,最後再由金屬閘極包覆,示意圖如下。

資料來源:IEEE Spectrum

一旦 GAA FET 技術發展成功(2025 年會有產品量產),接下來面臨的挑戰就是因為電晶體數量快速上升後,過往將訊號線路及供電網路都佈在晶圓正面的做法,就會碰到極限,除了空間不夠造成供電與訊號線路互相干擾外,持續向上增加高度也會造成訊號及電力損失,不利於能源效率的提升,因此,伴隨著 GAA FET 發展而來的另一項值得大家關注的技術方向,就是晶背供電。

A16 製程(16Å, below 2nm)開始,晶背供電將成為未來先進製程的標準做法。

製程微縮塞入更多的電晶體,就是為了要提供更強大且省電的算力,其他一般的應用其實不需要如此先進的製程,因此,設想在這樣的使用場景下,其訊號線路的複雜度、供電線路的密度都會大幅提升,而要在速度以及能耗效率上取得平衡,可斷定晶背供電(Backside power delivery network, BSPDN)是必然發展趨勢(TSMC 稱其技術為 Super Power Rail, SPR;Intel 則是 PowerVia)。

透過利用晶片背部的空間來佈供電線路,除了減少都佈在正面所需要空間外,也可以減少供電的傳輸距離,減少能量浪費,降低整體晶片的能耗,符合節能減碳的需求。而單獨把供電線路移到背面,也可增加導線間的線寬,在製程上就毋須使用昂貴的 EUV 製程,可進一步降低整體製造成本,對先進製程的普及至關重要。

因此,要觀察晶背供電開始大量應用時間點,就是進到 2nm 以下製程節點的時間點(改以 Å 為單位的製程),目前一般業界預估是在 2026 年可以看到量產,對於投資人而言,還有時間提早對相關類股進行佈局。

以下簡單說明早期晶背供電所新增加的製程,以及可能會用到的設備與耗材。

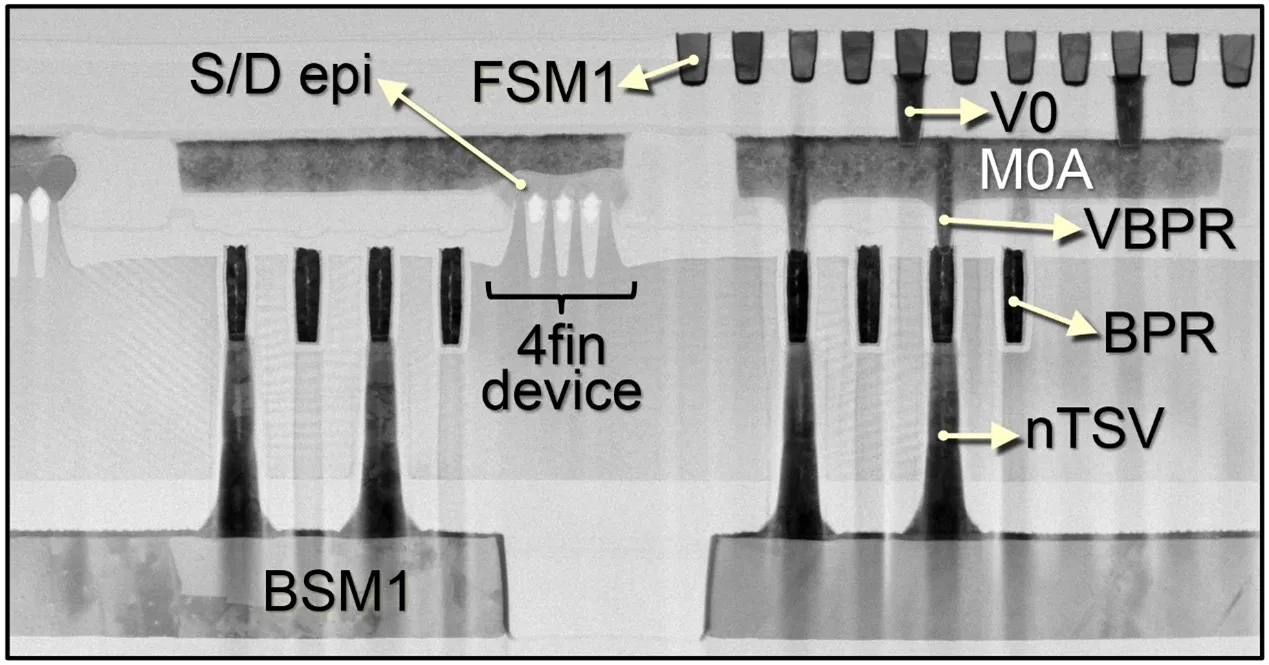

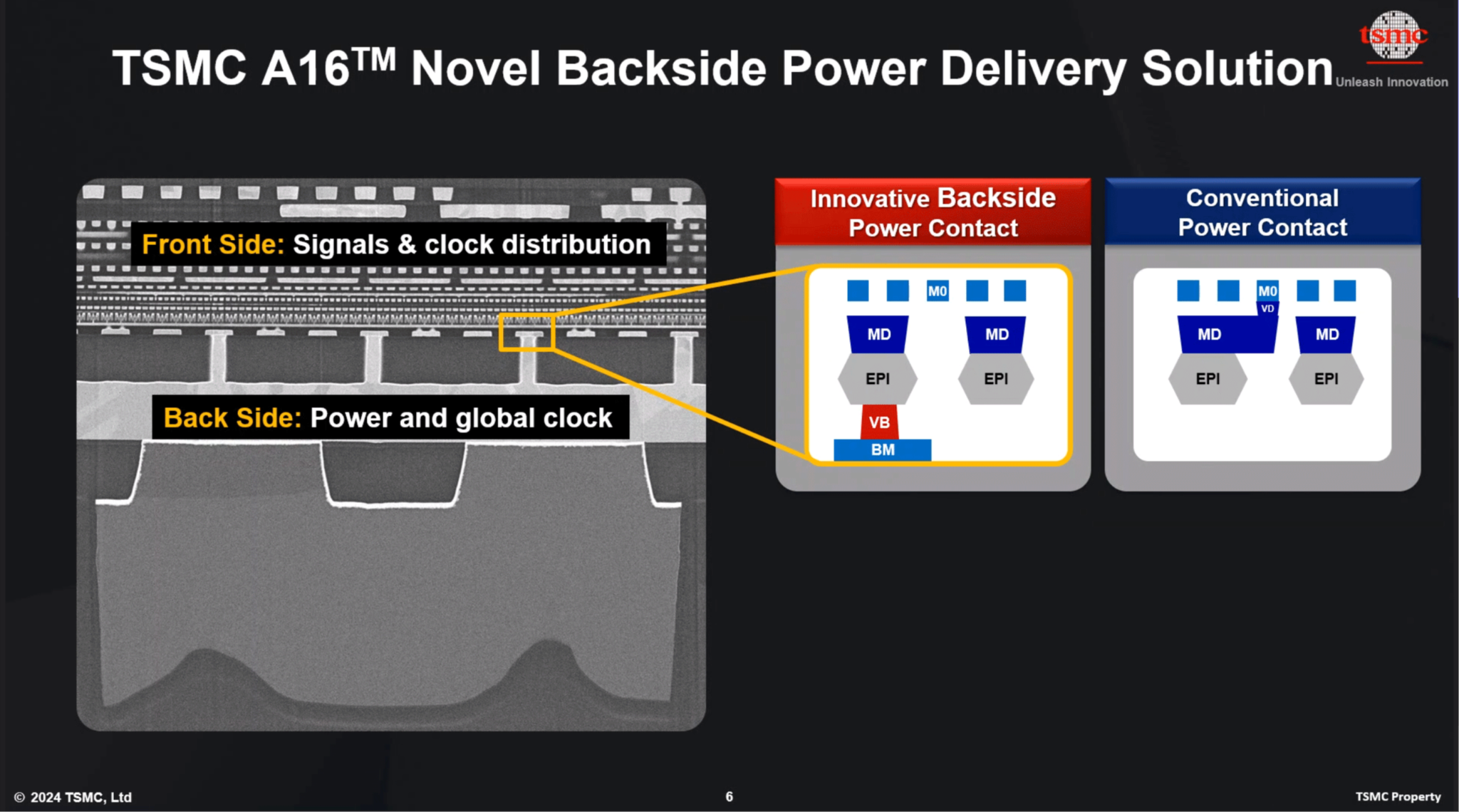

供電線路主要是連結到電晶體的源極(source, S)以及汲極(drain, D),簡稱 S/D,目前常見的做法是有三:一種是透過在電晶體製造時就預先埋入電源軌(buried power rail, BPR),再從晶片的背面,透過「奈米」矽穿孔(nano-TSV, nTSV)技術,從晶片的背面把供電傳到電晶體上,這種做法的好處是複雜度較低;第二種是不使用電源軌,而是在製作電晶體的時候,就把一系列的 nTSV 孔製備好,之後會把金屬填充進去作為導體,其概念是直接使用 nTSV 連結背面的供電網路層與電晶體層,Intel 的 PowerVia 是採這個做法;第三種是透過背部的供電接觸點,將背面電源傳輸網路直接連接到電晶體的源極與汲極(S/D epi),目前了解台積電的 SPR 即是採用這個模式,這樣的模式製造最複雜 ,但優點是在面積以及能效上可以更好。

然不論哪一種做法,都需要把原本長電晶體層的矽晶圓背面打磨成非常薄,讓背面的供電網路可以以最短的路徑連結到電晶體層,這也是為什麼國內兩大家晶圓減薄的廠商如昇陽半 (市:8028)、中砂(市:1560)會是大家常聽見有關晶背供電的概念股。

BPR 連接圖

台積電晶背供電方案示意圖

資料來源:台積電技術簡報

除了新增晶圓薄化製程外,晶背供電在 TSV 製程的應用上也會增加,TSV 製程一般包含晶圓薄化、鑽孔、介電材料沉積、導電材料填孔、晶圓連接等,其中,介電材料與導電材料沉積,過去大多是採用化學氣相沉積(Chemical Vapor Deposition, CVD)的做法,隨著製程的演進(孔徑更小、縱寬比 Aspect ration, AR 更大),在沉積製程的技術選擇上,原子層沉積(Atomic Layer Deposition, ALD)技術非常適合用在高深寬比(高 AR 值)的結構,且覆蓋率極佳(Step coverage),同時又可以在原子級的精準度下控制膜厚與沉積出非常細密的薄膜,除了非常適合用在 GAA FET 在長環繞的介電材料與包覆金屬材料外,在 nTSV 的製造上,隨著製程微縮、晶背供電的普及,ALD 相關的製程有機會可以更加普及,過往這類前端製程的設備多由國外大廠(如 ASM 或美國應材等)提供,近年來隨供應鏈去全球化的趨勢下,台灣本土的設備廠如天虹(市:6937),相關細節可參考【個股分析】半導體設備廠「天虹科技」,如何受惠設備國產化 及先進製程/封裝趨勢?,一旦通過認證,需求有機會大幅增加。

閱讀進度